P4

We are actively investigating the power of P4 language for specifying the packet processing operations:

- Header parsing

- Decision making (lookup tables, ACLs etc.) and the related actions (packet modifications)

- Modified packet assembly (deparsing)

We are also working on generic configuration API in C language which is then used for the configuration and control of generated P4 pipelines.

Related publications

- Pavel Benáček, Viktor Puš, Hana Kubátová: Automatic Generation of 100 Gbps Packet Parsers from P4 Description. In: First International Workshop on Heterogeneous High-performance Reconfigurable Computing, Austin, US, 2015.

- Pavel Benáček, Viktor Puš, Hana Kubátová: P4-to-VHDL: Automatic Generation of 100Gbps Packet Parsers. In: Proceedings of 2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM2016), Washington, USA, 2016.

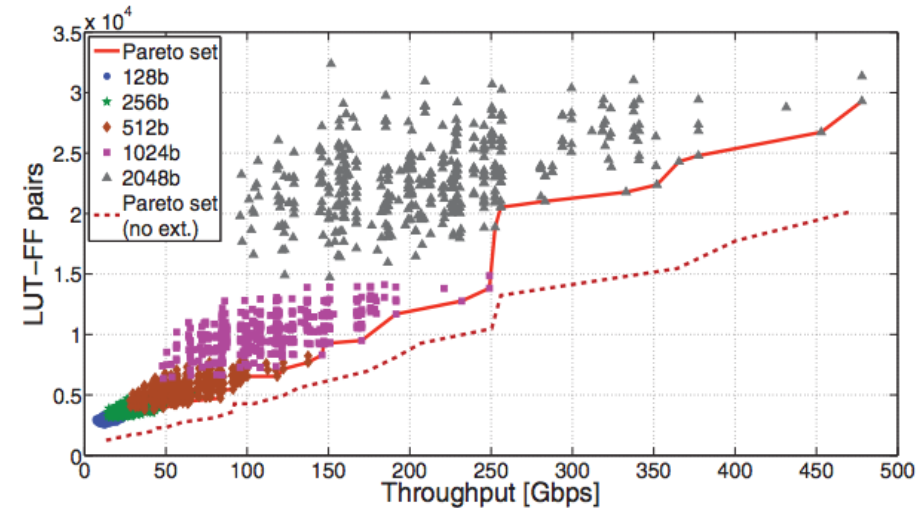

- Our results show that it is possible to generate packet processing circuits beyond 100 Gbps for Virtex-7 FPGAs:

- Pavel Benáček, Viktor Puš: The P4 Language as the Future of SDN [CZ]. Online at CESNET blog and root.cz (part 1, part 2), 2016.

- Pavel Benáček, Viktor Puš : P4-to-VHDL: Generating High Speed Network Devices. In: P4 Workshop, Stanford, California, USA, 2016.

- Pavel Benáček, Viktor Puš, Hana Kubátová, Tomáš Čejka: P4-to-VHDL: Automatic Generation of High-Speed Input and Output Network Blocks. In: Microprocessors and Microsystems journal (MICPRO, Volume: 56), DOI: 10.1016/j.micpro.2017.10.012., Elsevier, 2018.

- P. Benáček, V. Puš, J. Kořenek and M. Kekely: Line rate programmable packet processing in 100Gb networks. In: 27th International Conference on Field Programmable Logic and Applications (FPL), Ghent, 2017, pp. 1-1. DOI: https://doi.org/10.23919/FPL.2017.8056835.

- Pavel Benáček: Generation of High-Speed Network Device from High-Level Description. Dissertation thesis, Czech Technical University in Prague, Faculty of Information Technology, 2016.

- Pavel Benáček, Viktor Puš, Michal Kekely, Lukáš Richter, Pavel Minařík, Jan Pazdera: 100G In-Band Network Telemetry with P4 and FPGA. In: P4 Workshop, Stanford, CA, USA, 2017.

- Jakub Cabal, Pavel Benáček, Lukáš Kekely, Michal Kekely, Viktor Puš, and Jan Kořenek: Configurable FPGA Packet Parser for Terabit Networks with Guaranteed Wire-Speed Throughput. In: Proceedings of the 2018 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA ’18). ACM, New York, NY, USA, 249-258. DOI: https://doi.org/10.1145/3174243.3174250.

Use Case Studies

Header Parser Case Study

Adding TRILL protocol support into our HANIC and SDM firmware took two weeks in total, including roughly 1 day of manual modifications and verifications of header parser VHDL code. The modification of same-functions P4-generated header parser took around 15 minutes of writing P4 code only.

“IPv7” Processing

Adding the support of not existing protocol into our P4 capable FPGA design, including the implementation of control tool using our generic control and configuration API. This use case was published at FPL 2017 in Ghent, LinuxDays 2017 in Prague and the Conferention of CESNET’s E-Infrastructure in Prague. More details are available in our paper: P. Benáček, V. Puš, J. Kořenek and M. Kekely: Line rate programmable packet processing in 100Gb networks. In: 27th International Conference on Field Programmable Logic and Applications (FPL), Ghent, 2017, pp. 1-1. DOI: https://doi.org/10.23919/FPL.2017.8056835.

INT Processing

In-Band Network Telemetry (INT) is a relatively new concept of network performance monitoring, utilizing modern programmable data path elements. INT allows the tracing of exact path that a packet took, together with the internal status of data path elements it has visited. Our live demo showed a proof of concept implementation of a line rate 100 Gbps P4-programmed INT traffic sink – the point where INT marked traffic is received and the INT headers are processed. The FPGA equipped card with Xilinx Virtex-7 FPGA was chosen as hardware target. Our P4 to VHDL compiler is used to generate the packet processing pipeline that strips INT headers away from the packets. The cleaned traffic is forwarded by the card to the network. Therefore, the final traffic destination is not aware that INT was in progress and suffers no INT processing overhead. This demonstration was presented at P4 Workshop in 2017.